Design Flow

An Evolution in Digital Design

The evolution of hardware design has witnessed a significant shift from manually placing and wiring transistors to using automated design tools, known as Electronic Design Automation (EDA). These tools have become increasingly sophisticated, empowering designers to operate at higher levels of abstraction. Instead of detailing the layout of individual transistors, designers can now describe digital circuits using a specialized language, and EDA tools automatically translate these abstract specifications into a physical layout.

This evolution has played a pivotal role in accommodating the growing density of components on integrated circuits, progressing from Small-Scale Integration (SSI) with a few dozen transistors to Very Large-Scale Integration (VLSI), Ultra-Large-Scale Integration (ULSI) and even Wafer-Scale Integration (WSI) with billions of transistors in advanced systems like modern processors, memory modules, and various accelerators for training artificial intelligence models.

Register Transfer Level (RTL) is a traditional high-level hardware description language used in digital design to capture the functionality and behaviour of a digital system. The RTL descriptions focus on the data flow between registers and the operations performed on that data. The description defines how data moves from one register to another and how operations are executed in response to clock pulses. RTL is an abstraction level that sits between the behavioural level, where the system's functionality is described algorithmically, and the gate level, where the actual logic gates and flip-flops are defined.

From RTL to HLS

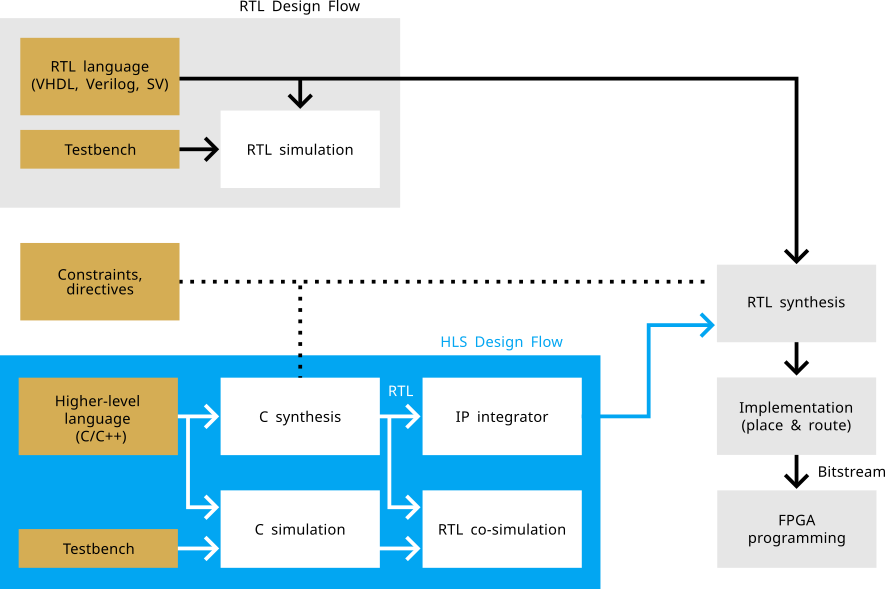

RTL descriptions in a language such as Verilog, SystemVerilog, or VHDL serve as the basis for further steps in the RTL design flow, including simulation, synthesis and implementation, guiding the translation of high-level functionality into a digital circuit. The upper part of the following image depicts traditional design flow using RTL for programming FPGA devices.

High-Level Synthesis (HLS) emerges as an even higher-level description technique in digital design. HLS allows designers to express the functionality of a digital system at a more abstract level, typically using C/C++ or similar high-level programming languages. HLS tools automatically convert code in higher-level language into hardware, reducing the manual effort involved in the design process. HLS bridges algorithmic description and hardware implementation, offering a more intuitive way to design and optimize complex digital systems.

We will use the AMD Vitis tool for HLS during this workshop. The process is depicted in the lower part of the upper figure and goes as follows:

- Functional verification of the C/C++ code using C simulation.

- C synthesis that translates code in higher-level language into RTL (VHDL/Verilog), considering constraints and optimization directives.

- RTL verification using the RTL co-simulation feature.

- Packaging the RTL implementation files as an intellectual property (IP) block using an IP integrator tool.

- Using IP block as an input to RTL synthesis, implementation, and FPGA bitstream generation process. Bitstream is a configuration file that is used to program the FPGA device.

Benefits of HLS

To summarize, let's write down several benefits that HLS brings to the digital design process:

- Higher level of abstraction: Designers can express hardware functionality using high-level programming languages, providing a more abstract and intuitive representation of algorithms.

- Productivity enhancement: HLS enables a more productive design process by leveraging familiar and expressive programming languages, reducing the need for manual RTL coding. Thus, it significantly accelerates time-to-market (TTM).

- Optimized performance and resource utilization: HLS tools automatically explore parallelism in algorithms and performance optimizations (pipelining, loop unrolling), maximizing hardware resource utilization and optimizing performance.

- Improved robustness: HLS tools enhance the robustness of designs by automatically handling low-level details, reducing the likelihood of human errors common in manual RTL coding.

- Less code:: Compared to traditional RTL flow, HLS often results in less code to maintain (about 20× less), simplifying design updates and modifications.

- Code reusability: HLS promotes code reuse, facilitating the integration of existing software components into hardware designs, which can lead to more efficient and scalable development.

Performance vs. throughput

Throughput is the rate of specific actions achieved per unit of time (e.g., liters per hour, gigabits per second). Performance is defined as higher throughput with low power consumption. Sometimes, we refer to performance as performance per watt.

To harvest all the mentioned advantages of HLS, we need to learn some fundamental principles and paradigms. So, let's move to the next section.